**IJCRT.ORG**

ISSN: 2320-2882

# INTERNATIONAL JOURNAL OF CREATIVE **RESEARCH THOUGHTS (IJCRT)**

An International Open Access, Peer-reviewed, Refereed Journal

# Single Source Cascaded H-Bridge Multilevel **Inverter Using Switched Capacitor**

Supriya.A.Baluwale, Shri.Manish.Rathi

M.Tech Power Electronics, Associate Professor

**Department of Electrical and Electronics**

PDA College of Engineering, Kalaburgi, (Karnataka)

## **ABSTRACT**

This paper present a single source cascaded H-bridge multilevel inverter using switched capacitor. The multilevel inverter consists of some of the series connected H-bridge cells. Where each cell required a separate dc source supply. Whereas in this topology separate dc source is replaced by switched capacitor with single dc source supply. Thus by using this method we can reduce the current spike which is harmful while charging the capacitor and it also provide zero current switching condition for charging the switch. The software used for this experiment is Mat lab/SIMULINK. The simulation result for nine level multilevel inverter using switched capacitor is described.

Keyword: Cascaded Multilevel Inverter, PI controller.

#### I. INTRODUCTION

Multilevel inverter is widely in modern electrical power system compared to two level inverter. The multilevel inverter are applicable in photovoltaic power conversion STATCOM, industrially machine drive, electric vehicles etc.., The main advantage of using multilevel inverter is firstly it provide high quality of output voltage waveform secondly it provide low harmonic distortion and lastly it also provide lower electromagnetic interference. The multilevel inverter is classified into three types namely neutral point clamped multilevel inverter, flying capacitor multilevel inverter and cascaded H-bridge multilevel inverter. Neutral point clamped multilevel inverter is also called diode clamped multilevel inverter introduced by Nabael were it is three level inverter. After this flying capacitor is introduced were it provide several switching state that help in controlling the capacitor voltage but the main drawback of this inverter is that the control system is very complicated as number of voltage level increases thus it required more number of capacitor. Hence to overcome drawback of neutral clamped and flying capacitor multilevel inverter the cascaded H-bridge multilevel inverter is introduced.

In this cascaded H-bridge multilevel consist of some the power semiconductor devices and isolated dc supply. The H-bridge cells are connected in series with each other with separate dc source supply. The combination of capacitor and switches is called as Hbridge with separate input dc source for each cell. Therefore cascaded H-bridge multilevel inverter require less number of components and also he control system is simple compared to neutral clamped and flying capacitor multilevel inverter. The main disadvantage of this multilevel inverter is that it requires several isolated dc source. By considering the above issue some of researchers try to reduce the number of dc source in cascaded multilevel inverter. One of the solutions is using single phase low frequency transformer instead of several dc source in order to provide a large number of output voltage level but the output voltage is determined by input dc voltage and transformer turns ratio thus proper transformer ratio must be chosen, they provide a galvanic isolation. The drawback of this method is that the system is bulky and expensive. The other solution is using a high frequency link and transformer to provide a supply to several dc sources. Although by using this method it reduces the total size, it requires extra number of component to develop the high frequency link and several isolated dc source.

The present paper proposed a single source cascaded H-bridge multilevel inverter using switched capacitor. In this proposed paper replacing the several isolated dc sources by switched capacitor with single dc source. This proposed paper presents some of the feature: 1.It use single dc source and the rest of the dc source are replaced by some of the capacitor. 2. It as self balancing capability. 3. It reduces the leakage current 4. It produces low harmonic distortion.5. It has ability to boost the staircase ac voltage.

#### II. PROPOSED SYSTEM CONFIGURATION

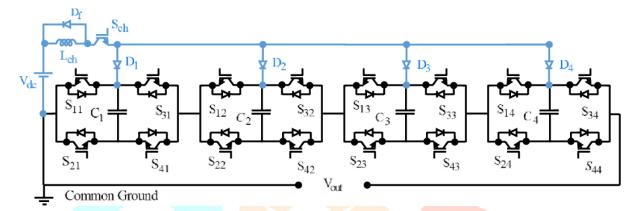

The proposed charging structure is in the below figure (1). It consists of two parts namely: the main part and charging unit respectively. The main parts consist of four conventional cascaded multilevel inverter and the charging unit consists of DC source, charging inductor Lch, charging switch Sch, freewheeling diode Df and some of the charging diodes Dn. The main part is represented by back and charging unit is shown by blue line. With help of charging inductor the charging unit charges the capacitor.

Figure 1: Nine level Cascaded H-bridge multilevel inverter with charging unit

This paper present nine level cascaded multilevel inverter. The structure consist of 16 switches were all the lower switches of H-bridge are complimentary of upper switches. It provides a common ground between dc and ac sides respectively. The table 1 represents the states of components and switching pattern of the voltage level in the configuration.

| levels | main switches                                                                          | Charging<br>switch | Charging<br>Diodes   | Capacitors           |

|--------|----------------------------------------------------------------------------------------|--------------------|----------------------|----------------------|

|        | $S_{11}$ , $S_{31}$ , $S_{12}$ , $S_{32}$<br>$S_{13}$ , $S_{33}$ , $S_{14}$ , $S_{34}$ | $S_{ch}$           | $D_1,D_2,$ $D_3,D_4$ | $C_1, C_2, C_3, C_4$ |

| 4      | 01010101                                                                               | 1                  | 1000                 | C,D,D,D              |

| 3      | 00010101                                                                               | 1                  | 1100                 | C,C,D,D              |

| 2      | 00000101                                                                               | 1                  | 1110                 | C,C,C,D              |

| 1      | 00000001                                                                               | 1                  | 1111                 | C,C,C,C              |

| 0      | 00000000                                                                               | 1                  | 1111                 | C,C,C,C              |

| -1     | 10000000                                                                               | 0                  | 0000                 | D,N,NN               |

| -2     | 10100000                                                                               | 0                  | 0000                 | D,D,N,N              |

| -3     | 10101000                                                                               | 0                  | 0000                 | D,D,D,N              |

| -4     | 10101010                                                                               | 0                  | 0000                 | D,D,D,D              |

Table 1: Operating state of components

The level shifted sinusoidal pulse width modulation strategy is the most compatible strategy for this topology. Since the charging structure operated during positive cycle and rest during negative cycle. The capacitor nearer to dc source will charge quickly and followed by other capacitor i.e., C1, C2, C3 &C4. In the proposed system PI controller is used in order to reduce the harmonic distortion. The charging inductor only charge during positive cycle. The value of charging inductor must be chosen such as way that it must charge quickly and discharge slowly. The value of charging inductor is calculated as follows:

$$L_{ch} = \frac{1}{(2\pi f)^2 \alpha C}$$

#### III. SIMULATION RESULTS

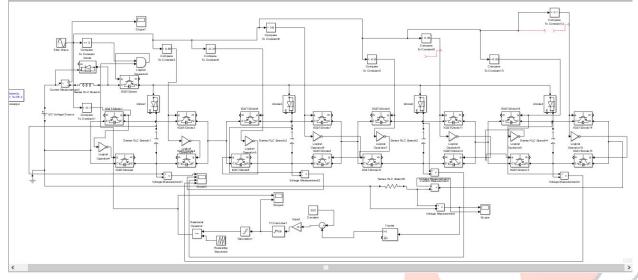

Simulation of the proposed topology is performed by using MATLAB/SIMULINK software. The simulation for a nine level cascaded multilevel inverter with single dc source is shown in Fig.2 with two different input voltages with pure resistive load. By using PI controller the harmonic present in output voltage is reduced. The parameter used in the simulation for proposed topology is given in below table (2)

| Parameter         | Rating  |

|-------------------|---------|

| Input dc voltage  | 80v     |

| Charging inductor | 1.3mH   |

| Capacitor         | 10mF    |

| Resistive load    | 1600ohm |

| Duty cycle        | 0.8     |

| Output power      | 100W    |

| Output voltage    | 340v    |

Figure 2: Simulation circuit diagram

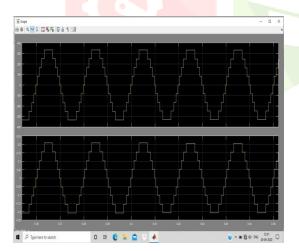

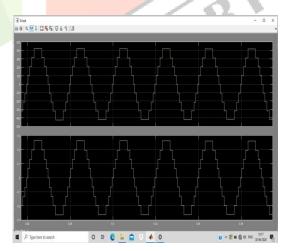

The output voltage and load current waveform for input voltages of 80v and 100v shown in Fig.3. (a) & (b)

Figure 3(a) & (b) output voltage and load current for two different input voltages of 80v and 100v.

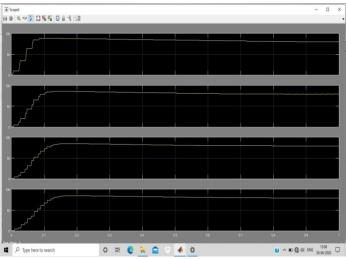

The charging current of capacitor waveform shown in Figure: 4 indicate the spikes of the charging current are mitigated so the capacitor are smOothly charged.

Figure 4: voltage of each capacitor.

#### IV. CONCLUSION

The single source cascaded H-bridge multilevel inverter with switched capacitor for nine levels with different input voltage is tested. In order to eliminate the several isolated dc sources which is one of the main disadvantage of cascaded multilevel inverter is overcome by using switched capacitor with PI controller. By using single dc voltage source it is able to boost the staircase ac voltage. By this method it can reduce the power losses, reduce in the output current harmonic distortion and voltage ripple are expected to be minimum.

## **REFERENCES**

- [1] J. Rodriguez, J. Sheng Lai, F. Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Trans Ind. Electron., vol. 49, no. 4, pp.724-738, Aug. 2002.

- [2] S. G. Song, F. S. Kang, S. J. Park, "Cascaded multilevel inverter employing three-phase transformers and single dc input," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 2005-2014, June 2009.

- [3] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a single-phase cascaded H-bridge multilevel inverter for grid connected photovoltaic systems," IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4399-4406, Nov,2009

- [4] J. Rodriguez, S. Bernet, P. K. Steimer, I. E. Lizama, "A survey on neutral-point-clamped Inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2219-2230, July 2010.

- [5] J. Pereda, J. Dixon, "High-frequency link: A solution for using only one de source in asymmetric cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 58, no. 9, pp. 3884-3892, Sep. 2011.

- [6] J. Pereda, J. Dixon, "23-level inverter for electric vehicles using a single battery pack and series active filters," IEEE Trans. Veh. Technol., vol. 61, no. 3, pp. 1043 – 1051, Feb. 2012.

- [7]M. R. Banaei; H. Khounjahan, E. Salary. "Single-source cascaded transformers multilevel inverter with reduced number of switches," IET Power Electron. vol. 5, no. 9, pp. 1748-1753, Nov. 2012.

- [8] A. K. Rathore, J. Holtz, T. Boller, "Generalized optimal pulse width modulation of multilevel inverters for low-switching frequency control of medium-voltage high-power industrial ac drives," IEEE Trans. Ind. Electron., vol. 60, no. 10, pp. 4215-4224, Oct. 2013.

- [9] V. Sonti, S. Jain, S. Bhattacharya, "Analysis of the Modulation Strategy for the Minimization of the Leakage Current in the PV Grid-Connected Cascaded Multilevel Inverter," IEEE Trans. on Power Electron., vol. 32, no. 2, pp.1156-1169, Feb. 2017.

- [10] M. Malinowski, K. Gopakumar, J. Rodriguez, M. A. Perez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197-2206, July 2010. lectron., vol. 32, no. 2, pp.1156-1169, Feb. 2017.